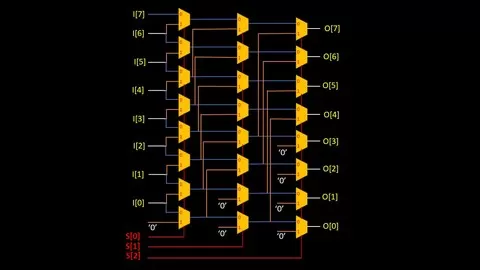

Most of the 21st-century applications require powerful hardware but also along with the centralized controller allowing the development of complex algorithms. As we enter into the AI or Cloud-based devices and as systems complexity is growing daily, the need for incorporating multiple processor instances becomes mandatory as we progress in the AI era. Zynq and Microblaze are two popular alternatives that exist in the market suitable for almost any application requirements. The requirements of using Multiple instances of Processor viz. Multiple instances of Microblaze soft processor or using a hard processor such as Zynq Processor along with single or multiple instances of Microblazer become necessary to independently handle both Data processing and control requirements. The fundamental challenge of incorporating multiple instances of Soft processors like Microblaze is the number of resources consumed for implementing Microblaze on the FPGA. Since FPGA consists of a limited amount of the FPGA resources, hardware and Software partition plays a prominent role in building complex systems. Another popular alternative approach followed by Embedded Engineers to build a Custom CPU / Processor with the only required functionality thereby saving a large amount of the resources as compared to adding Microblaze instance. The course will discuss all the fundamentals required to build a simple processor/ CPU with Verilog HDL and strategies to test its functionality. After completing this course, you will understand all the necessary skills required to build Complex CPU architecture to meet requirements. Best wishes for crafting your own processor.

Courses » IT & Software » Hardware » Verilog HDL Programming » Designing a Processor with Verilog HDL and Xilinx Vivado

Disclosure: when you buy through links on our site, we may earn an affiliate commission.

Designing a Processor with Verilog HDL and Xilinx Vivado

Step by Step Guide from Scratch

Created by

8.7

CourseMarks Score®

Freshness

Feedback

Content

Top Verilog HDL Programming courses:

Detailed Analysis

CourseMarks Score®

CourseMarks Score® helps students to find the best classes. We aggregate 18 factors, including freshness, student feedback and content diversity.

Freshness Score

Course content can become outdated quite quickly. After analysing 71,530 courses, we found that the highest rated courses are updated every year. If a course has not been updated for more than 2 years, you should carefully evaluate the course before enrolling.

Student Feedback

New courses are hard to evaluate because there are no or just a few student ratings, but Student Feedback Score helps you find great courses even with fewer reviews.

Content Score

The top online course contains a detailed description of the course, what you will learn and also a detailed description about the instructor.

Tests, exercises, articles and other resources help students to better understand and deepen their understanding of the topic.

This course contains:

Table of contents

Description

You will learn

✓ Buliding Custom Intruction Set to meet resource utilizations

✓ Strategies to add Program and Data Memory inside Processor

✓ Strategies to add Jump and Branching Instructions inside Processor

✓ Strategies to include Register, Direct and Immediate addressing modes to processor

✓ Crafting your own processor from Scratch similar to Popular Intel 8051 architecture

Requirements

This course is for

How much does the Designing a Processor with Verilog HDL and Xilinx Vivado course cost? Is it worth it?

Does the Designing a Processor with Verilog HDL and Xilinx Vivado course have a money back guarantee or refund policy?

Are there any SCHOLARSHIPS for this course?

Who is the instructor? Is Kumar K. a SCAM or a TRUSTED instructor?

8.7

CourseMarks Score®

Freshness

Feedback

Content